## FC7300Fxx Product Brief

[FC7300F8MDT, FC7300F4MDD, FC7300F4MDS]

The FC7300F8MDT, FC7300F4MDD, and FC7300F4MDS constitute the FC7300 family of microcontrollers with diverse memory sizes, packages, and peripherals for design scalability.

The FC7300 product series extends the FC4150 family in the automotive industry with the Arm Cortex-M7 core at higher performance, larger memory, and ASILD rating. It also supports security requirements including the secure boot and EVITA full. The FC7300 is suitable for a wide range of applications in automotive.

#### **Target Applications**

- Domain/Zonal controller

- Chassis domain

- Advanced Driver Assistant System (ADAS)

- Active suspension control system

- One-box

- EV main inverter

- Motor control

- Sensor fusion

- 800/400V Battery Management System (BMS)

- Gateway

- Electric Power Steering (EPS)

- Electronic Stability Control (ESC)

- Anti-lock Brake System (ABS)

- Auto Parking Assist (APA)

## **Key Features**

- 32-bit ARM® Cortex®-M7 core (Multi)

- Up to 300 MHz execution speed

- Up to 8 MB PFlash, 256 KB DFlash, and 1088 KB RAM

- Temp Grade1/-40°C to +125°C

- ISO 26262 ASIL-D support

- Package: 176LQFP-EP and BGA320

## 1 Block Diagram

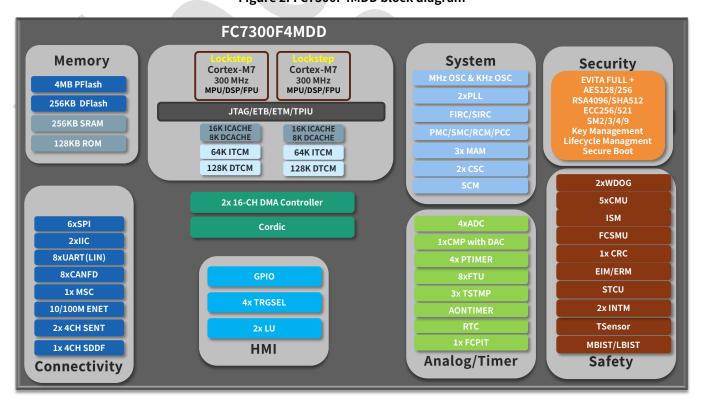

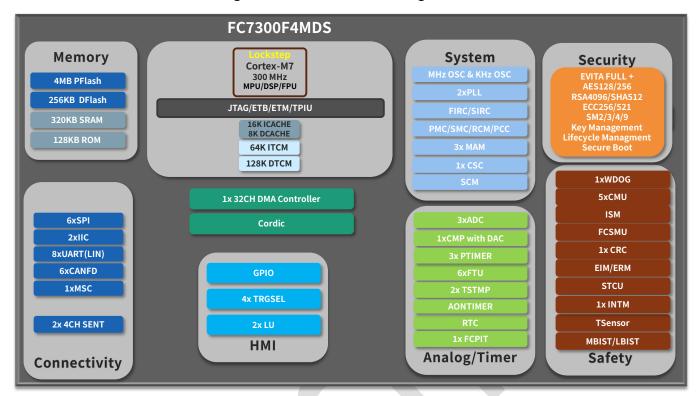

The following figures show the block diagrams of the FC7300 family. For a detailed comparison, refer to <u>Table 1. FC7300 feature</u> list.

FC7300F8MDT Memory System Security Cortex-M7 Cortex-M7 Cortex-M7 300 MHz MPU/DSP/FPU 300 MHz MPU/DSP/FPU 300 MHz MPU/DSP/FPU EVITA FULL + AES128/256 8MB PFlash 256KB DFlash JTAG/ETB/ETM/TPIU 512KB SRAM 16K ICACHE 8K DCACHE 16K ICACHE 8K DCACHE 16K ICACHE 8K DCACHE 64K ITCM 64K ITCM 64K ITCM **128K DTCM 128K DTCM 128K DTCM** 3xWDOG 5xCMU 2x 32CH DMA Controller 1xOSPI ISM 8xSPI Cordic **FCSMU** 2xIIC 2x CRC 18xUART(LIN) EIM/ERM 10xCANFD **GPIO** STCU 2xMSC **4x TRGSEL** 1G ENET with TSN 3x INTM **TSensor** 2x 4CH SENT 2x LU MBIST/LBIST 1x 4CH SDDF **HMI** Analog/Timer Safety Connectivity

Figure 1. FC7300F8MDT block diagram

Figure 2. FC7300F4MDD block diagram

Figure 3. FC7300F4MDS block diagram

#### 2 Features

The FC7300 product series has the following features:

#### 2.1 Overview

#### • Operating Environment

- Voltage range: 3.0 V to 5.5 V

- Support separated 3.0 V and 5.5 V IO rings

- Ambient temperature range: -40°C to +125°C; junction temperature: -40°C to +150°C

#### Arm Cortex-M7 Core

- 300 MHz frequency with 3.23 Dhrystone MIPS per MHz

- Army7 Architecture and Thumb-2 ISA

- Digital Signal Processing (DSP) instruction

- Single-precision Floating Point Unit (FPU)

- Configurable Nested Vectored Interrupt Controller (NVIC)

- Support Memory Protection Unit (MPU) with 16 regions

- Each core has 16 KB ICACHE and 8 KB DCACHE

- Each core has 64 KB ITCM and 64 KB DTCM0 and 64 KB DTCM1

- **Up to three CM7 running cores (CPU0/1/2)**: CPU0 and CPU1 with extra checker cores (CPU3/4) to form lockstep operation. The lockstep monitor also covers the CM7 AXI2AHB and ITCM/DTCM0&1 ECC logic.

- CORDIC accelerator for mathematical operations such as angles

- Mailbox (MB) with up to 16 communication channels and 4 interrupt channels for on-chip CPU and HSM;

support the hardware semaphore function.

- Three Matrix Access Monitors (MAMs), which monitor all on-chip matrix access, and support watchdog timeout function for matrix access.

- Up to three Core System Control (CSC) modules; used for the stop mode related handle etc. control.

- One System Control Module (SCM); used for the on-chip connection control, lock step control, CPU low power status, interrupt routing control, etc.

- One Security Controller (SEC); used for on-chip debug/test mode/lifecycle related control.

- Up to two 32-channel Direct Memory Access (DMA) modules with selectable DMA sources.

#### Clock Sources

- 16 48 MHz Fast Oscillator (FOSC) with up to 50 MHz DC external input clock in bypass mode

- 32 kHz Slow Oscillator (SOSC)

- 96 MHz Fast Internal RC Oscillator (FIRC96M)

- 12 MHz Slow Internal RC Oscillator (SIRC12M)

- 32 kHz Slow Internal RC Oscillator (SIRC32k)

- Up to 300 MHz Phased Lock Loop (PLL0 and PLL1) with the reference clock from FIRC48M or FOSC

#### Power Management

- Four power modes: RUN, WAIT, STOP and Standby. Optional 64 KB System RAM retention in standby mode.

#### Memory

- Up to 8 MB program flash memory with Address and Data Single-bit Error Correction and Double-bit Error Detection (SECDED)

- Up to 256 KB data flash memory with Address and Data SECDED

- Up to 512 KB SRAM with Address and Data SECDED

- One Octal Serial Peripheral Interface (OSPI) with up to 75 MHz DDR support. (Only available for FC7300F8MDT)

- 128 KB ROM with Address and Data SECDED, which contains CM7 core self-test/flash program & erase/ Hardware Secure Module (HSM) secure boot etc.

#### Analog

- Up to four 12-bit Successive Approximation (SAR) Analog-to-Digital Converters (ADCs) with up to 32 channel analog inputs per module

- Up to three Analog Comparators (CMPs) with internal 8-bit Digital-to-Analog Converter (DAC)

#### • Debug Functionality

- Serial Wire/JTAG Debug Port (SWJ-DP) combines

- Data Watchpoint and Trace (DWT)

- Instrumentation Trace Macrocell (ITM)

- Embedded Trace Macrocell (ETM)

- Trace Port Interface Unit (TPIU) with up to 16-bit

- Flash Patch and Breakpoint (FPB) Unit

- Cross Trigger Interface (CTI)

- Embedded Trace Buffer (ETB)

- FUNNEL

- JTAG Test Access Port (TAP) and boundary scan support

#### • Human-Machine Interface (HMI)

- Up to 248 GPIO pins (excl. reset pin) with separated core interrupt support

- Non-Maskable Interrupt (NMI)

- GPIO interface with separated core control

#### • Communication Interfaces

- Up to 18 FC Universal Asynchronous Receiver/Transmitter (FCUART) modules with LIN support

- Up to eight FC Serial Peripheral Interface (FCSPI) modules; support 1/2/4 data lines and master/slave mode

- Two FC Inter-Integrated Circuit (FCIIC) modules

- Up to ten FLEXCAN modules with optional CAN-FD support

- One 10/100/1000 Mbps Ethernet with IEEE1588 and TSN, MII/RMII/RGMII support. (Not available for FC7300F4MDS)

- Up to two Micro Second Channel (MSC) modules

- Up to two 4-channel Sent Edge Nibble Transmit (SENT) modules

- Up to one 4-channel Sigma Delta Digital Filter (SDDF) module

- Four Trigger Selects (TRGSELs) for on-chip bus connection

- Two Lookup Unit (LU) modules; each supports 4 lookup tables

#### Security

- Hardware Secure Module (HSM) with crypto algorithms including AES/SM4/ECC/RAS/SHA/SM3/SM4/SM9

- EVITA full capability

- Support random number generation and pseudo random number generation

- Key import/export management

- Monotonic counter support

- Support secure boot and non-secure boot mode

- Support In-System Program (ISP) mode

#### Safety

- Up to five Clock Monitor Units (CMUs) for all internal critical root clock source monitor

- Power Management Controller (PMC) with LVR/LVD/HVD etc. on internal generate supply and external supply protection

- ECC with both address and data protection on ROM, flash and SRAM memories

- Memory Access Monitor on the system memory, including peripheral slots such as the APB bridge (AFCB0 and AFCB1)

- Up to two Cyclic Redundancy Check (CRC) modules

- Up to three internal Watchdogs (WDOGs) with window function

- One Error Injection Module (EIM) for ECC logic and lock step logic check

- One Error Reporting Module (ERM) for ECC-related monitor errors

- One Fault Control and Safety Management Unit (FCSMU) for on-chip error handling and optionally outputting the chip status to external pins

- LockStep Monitor for CPU0/1

- End-to-End ECC protection on all CPUx-related access paths

- One Safety Test Control Unit (STCU) for Logic BIST (LBIST) and Memory BIST (MBIST) controller

- One Interface Safety Monitor (ISM) module to monitor up to 16 delays/periods/duties of critical signals

- Up to three Interrupt Monitor (INTM) modules; each supports up to 4 channels and can monitor the interrupt keep-active timeout or interrupt generation timeout

- CM7 core self-test API in ROM code

#### Timers

- Up to 12 Flexible Timer Unit (FTU) modules with IC/OC/PWM function; FTU1/2/4/5 also support the Quadrature Decoder function

- One Always-on Timer (AONTIMER) with standby wake up capability

- Four Programmable Timers (PTIMERs)

- Two FC Programmable Interrupt Timers (FCPITs); each has 4 channels

- One Real-Time Clock (RTC)

- Up to four 56-bit Timer Stamps (TSTMPs) with four 32-bit compare channels, TSTMP0 runs at 1 MHz clock and TSTMP1/2/3 run at Bus clock

- One Frequency Measurement (FREQM) module; with up to 64 input clock sources

#### Package

- 320LFBGA and 176LQFP-EP package options

#### Qualification

- ASIL D certified according to ISO 26262

- AEC-Q100/Q006 Grade 1 (-40°C to 125°C)

### 2.2 Feature Comparison

The table below lists the differences in major features and peripheral counts of three chips from the FC7300 family.

Table 1. FC7300 feature list

| Features                                                  |            |                |       | Chips                                                               |                       |                       |  |

|-----------------------------------------------------------|------------|----------------|-------|---------------------------------------------------------------------|-----------------------|-----------------------|--|

|                                                           |            |                |       | FC7300F8MDT                                                         | FC7300F4MDD           | FC7300F4MDS           |  |

| Automotive cert. Temp. Grade                              |            |                | Grade | Grade1/ -40°C to +125°C                                             |                       |                       |  |

| Function Safety                                           |            |                |       | ASIL-D                                                              |                       |                       |  |

| Power Design Voltage Range  T <sub>A</sub> T <sub>J</sub> |            | 3.0 V to 5.5 V |       |                                                                     |                       |                       |  |

|                                                           |            | TA             |       | -40°C to +125°C                                                     |                       |                       |  |

|                                                           |            | TJ             |       |                                                                     | -40°C to +150°C       |                       |  |

| Fre                                                       |            | Core           |       | Cortex-M7; 2*Lockstep + 1                                           | Cortex-M7; 2*Lockstep | Cortex-M7; 1*Lockstep |  |

|                                                           |            | Frequency      |       |                                                                     | 300 MHz               |                       |  |

|                                                           |            | MPU            |       | Yes                                                                 |                       |                       |  |

|                                                           |            |                | E     | 16 KB                                                               |                       |                       |  |

|                                                           |            |                | HE    |                                                                     | 8 KB                  |                       |  |

|                                                           |            | PFlash/Bank    |       | 8 MB/4                                                              | 4 M                   | 1B/2                  |  |

|                                                           |            | DFlash         |       | 256 KB                                                              |                       |                       |  |

| Mem                                                       | ory        | ВАМ            | SRAM  | 512 KB                                                              | 256 KB                | 320 KB                |  |

|                                                           |            | RAM            | тсм   | 3 × 192 KB                                                          | 2 × 192 KB            | 192 KB                |  |

|                                                           |            | ROM            |       |                                                                     | 128 KB                |                       |  |

| Clock                                                     | Clock      |                |       | Multi clocks, including FIRC96M/SIRC12M/SIRC32K/FOSC48M/SOSC32K/PLL |                       |                       |  |

| Digital IOs                                               |            |                |       | Up to 248                                                           |                       |                       |  |

|                                                           | System     | СРМ            |       | Yes                                                                 |                       |                       |  |

|                                                           |            | DMA            |       | 2 × 32-channel                                                      | 2 × 16-channel        | 1 × 32-channel        |  |

|                                                           |            | WKU            |       | Yes                                                                 |                       |                       |  |

|                                                           |            | РМС            |       | Yes                                                                 |                       |                       |  |

|                                                           |            | SMC            |       | Yes                                                                 |                       |                       |  |

|                                                           |            | RGM            |       | Yes                                                                 |                       |                       |  |

|                                                           |            | SEC            |       | Yes                                                                 |                       |                       |  |

|                                                           |            | CORDIC         |       | Yes                                                                 |                       |                       |  |

| rals                                                      |            | csc            |       | 3                                                                   | 2                     | 1                     |  |

| Peripherals                                               |            | SCM            |       | Yes                                                                 |                       |                       |  |

| Per                                                       |            | МАМ            |       | 3                                                                   |                       |                       |  |

|                                                           | МВ         |                |       | Yes                                                                 |                       |                       |  |

|                                                           | Memory     | FMC            |       | Yes                                                                 |                       |                       |  |

|                                                           |            | ACC            |       | Yes                                                                 |                       |                       |  |

|                                                           |            | OSPI           |       | Yes No                                                              |                       |                       |  |

|                                                           | Clocking   | SCG            |       | Yes                                                                 |                       |                       |  |

|                                                           | Clocking   | PCC            |       | Yes                                                                 |                       |                       |  |

|                                                           | Function   | WDOG           |       | 3                                                                   | 2                     | 1                     |  |

|                                                           | Safety EIM |                |       |                                                                     | Yes                   |                       |  |

| Features                    |          |            | Chips           |                   |             |  |

|-----------------------------|----------|------------|-----------------|-------------------|-------------|--|

|                             | Feat     | ures       | FC7300F8MDT     | FC7300F4MDD       | FC7300F4MDS |  |

|                             |          | ERM        | Yes             |                   |             |  |

|                             |          | INTM       | 3               | 2                 | 1           |  |

|                             | Function | СМИ        |                 | 5                 |             |  |

|                             | Safety   | ISM        | Yes             |                   |             |  |

|                             |          | FCSMU      | Yes             |                   |             |  |

|                             |          | STCU       | Yes             |                   |             |  |

|                             | Security | CRC        | 2 1             |                   |             |  |

|                             | НМІ      | GPIO       | Yes             |                   |             |  |

|                             |          | PORT       | Yes             |                   |             |  |

|                             |          | TRGSEL     | 4               |                   |             |  |

|                             |          | LU         | 2               |                   |             |  |

|                             |          | ADC        | 4               |                   | 3           |  |

|                             | Analog   | СМР        | 3               |                   |             |  |

| ?                           |          | TMU        | Yes             |                   |             |  |

|                             |          | FTU        | 12              | 8                 | 6           |  |

| ;                           |          | FCPIT      | 2               | 1                 |             |  |

| •                           |          | TSTMP      | 4               | 3                 | 2           |  |

|                             | Timer    | RTC        |                 | Yes               |             |  |

|                             |          | AONTIMER   | Yes             |                   |             |  |

|                             |          | PTIMER     |                 |                   | 3           |  |

|                             |          | FREQM      |                 | Yes               |             |  |

|                             |          | FCSPI      | 8               | 6                 | )           |  |

|                             |          | FCIIC      |                 | 2                 |             |  |

|                             |          | FCUART     | 18              | 8                 | 3           |  |

|                             |          | FLEXCAN    | 10              | 8                 | 6           |  |

|                             | Comm.    | SENT       | 2               |                   |             |  |

|                             |          | SDDF       | Yes             |                   | No          |  |

|                             |          | MSC        | 2               | 1                 |             |  |

|                             |          | ENET       | Yes (1 Gbit)    | Yes (10/100 Mbit) | No          |  |

| Security                    |          |            | HSM, EVITA Full |                   |             |  |

| Package 176LQFP-EP 320LFBGA |          | 176LQFP-EP | Yes             |                   |             |  |

|                             |          |            | Yes             |                   |             |  |

# **Revision History**

| Revision | Date       | Changes                                                                 |  |

|----------|------------|-------------------------------------------------------------------------|--|

| 0.1      | 2023/07/14 | Initial release                                                         |  |

|          |            | Updated the three block diagrams in <i>Chapter 1 Block Diagram</i> ;    |  |

|          |            | In Section 2.2 Feature Comparison:                                      |  |

|          |            | ■ For FC7300F4MDD:                                                      |  |

|          |            | - Changed the DMA instance from "2 $	imes$ 32-ch" to "2 $	imes$ 16-ch"; |  |

|          |            | - Changed the CRC instance number from "2" to "1";                      |  |

|          |            | - Changed the CMP instance number from "3" to "1";                      |  |

|          |            | - Changed the FTU instance number from "10" to "8";                     |  |

|          |            | - Changed the FCPIT instance number from "2" to "1";                    |  |

|          |            | - Changed the FCUART instance number from "10" to "8";                  |  |

| 0.2      | 2024/09/25 | - Changed the FLEXCAN instance number from "6" to "8";                  |  |

|          |            | - Changed the MSC instance number from "2" to "1".                      |  |

|          |            | ■ For FC7300F4MDS:                                                      |  |

|          |            | - Changed the CMP instance number from "2" to "1";                      |  |

|          |            | - Changed the FTU instance number from "8" to "6";                      |  |

|          |            | - Changed the FCPIT instance number from "2" to "1";                    |  |

|          |            | - Changed the PTIMER instance number from "4" to "3";                   |  |

|          |            | - Changed the FLEXCAN instance number from "4" to "6";                  |  |

|          |            | - Changed the SENT instance number from "1" to "2".                     |  |

|          |            | Fixed typos                                                             |  |

#### **Contact Us**

#### **Headquarters:**

Room 213, 2nd Floor, Suite Z104, Building 2, NO.78, East Jinshan RD, New District, Suzhou, Jiangsu 215011, P.R. China **Website:** www.flagchip.com.cn

**TEL:** +86-512-66166689

#### Disclaimer

This document is the property of the Suzhou Flagchip Semiconductor Co., Ltd. (hereinafter referred to as "Flagchip"). Any information provided in this document is only for reference purposes.

Except as expressly provided herein, no part of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Flagchip. Flagchip hereby disclaims any responsibilities for any losses, expenses, claims, damages, and liabilities related to the use of the information. All information described herein is subject to change without further notice.

ARM and Cortex are registered trademarks of ARM Limited. All other trademarks mentioned in this document are the property of their respective owners.